# A Low Voltage Self-Biased and Bulk-Driven MOSFET Wilson Current Mirror Circuit

<sup>1</sup>Shobhna, <sup>2</sup>Mrs. Manpreet Kaur

<sup>1</sup>Student, M.TECH VLSI, <sup>2</sup>Assistant Professor

<sup>1</sup>Department of Electronics and Communication Engineering

<sup>1</sup>Chandigarh Engineering College, Landran, Punjab, India

Abstract- A current mirror is a circuit intended to duplicate a current through one gadget by controlling the current in another dynamic gadget of a circuit. Conceptually, a perfect current mirror is basically a perfect altering current enhancer that turns around the present bearing too or it is a current-controlled current source(CCCS). In this paper, various types of current mirrors are discussed and also Bulk-Driven MOSFET current mirror is discussed. Different capacities like current amplification, level shifting, biasing and stacking is driven by current mirror circuits. The execution of the current mirror circuits can be expanded by improving its Bandwidth, make it to take a shot at low voltage which will bring about low power dissipation.

Keywords- Wilson, Widlar, cascaded current mirror, Bulk-Driven, Gate-Driven.

#### I. INTRODUCTION

As the name of the circuit infers itself, current mirror circuits duplicate the current. The yield current of the circuit relies on the input current rather than input terminal voltage. The current mirror is used to give inclination streams and element weights to circuits. It can likewise be utilized to display a more reasonable current source (since ideal current source don't exist). There are various topologies for current mirror such as Widlar mirror and Wilson current mirror. Widlar mirror topology is one that shows up in numerous monolithic ICs. Wilson current mirror is a three-terminal circuit that acknowledges an information current at the input terminal and gives a "reflected" current source or sink yield at the output terminal. Basically there are three sorts of current mirrors: - Widlar current mirrors, Wilson current mirrors and Cascoded current mirrors.

The paper is organized as follows: Various types of current mirror circuits are discussed in Section-II, Section-III describes low voltage bulk-driven MOSFET current mirror for CMOS technology. Section-IV describes the conclusion of this paper.

## II. CURRENT MIRROR CIRCUITS TYPES

There are three types of current mirrors: - Wilson current mirrors, Widlar current mirrors and cascaded current mirrors.

#### 1. Widlar current source

A Widlar current source is a change of the fundamental two-transistor current reflect that fuses an emitter degeneration resistor for just the yield transistor, enabling the current source to produce low streams utilizing just direct resistor values. The Widlar circuit might be utilized with bipolar transistors, MOS transistors and even vaccum tubes. An illustration application is the 741 operational speaker and Widlar utilized the circuit as a section in numerous designs.

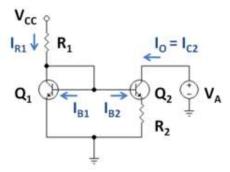

Figure-1 is an example Widlar current source utilizing bipolar transistors, where the emitter resistor R2 is associated with the yield transistor Q2 and has the impact of lessening the current in Q2 in respect to Q1.

Figure-1

The way to this circuit is that the voltage drop over the resistor R2 subtracts from the base-emitter voltage of transistor Q2, thereby killing the transistor contrasted with transistor Q1. This perception is communicated by comparing the base voltage expressions found on either side of the circuit in fig. - 1 as

$$V_B = V_{BE1} = V_{BE2} + (\beta_2 + 1) I_{B2} R_2$$

$$\Rightarrow$$

1/R<sub>2</sub> (V<sub>BE1</sub> - V<sub>BE2</sub>) = ( $\beta_2$  +1) I<sub>B2</sub>

Where  $\beta_2$  is the beta-estimation of the yield transistor, which is not the same as that of the information transistor, VBE alludes to base-emitter voltage. This conditions suggests

$$\begin{split} &(\beta_2 + 1) \; I_{B2} = (1 \, + \, 1/\beta_2) \; I_{C2} \\ &= 1/R_2 \, (V_{BE1} \text{--} \; V_{BE2}) \end{split}$$

$= V_T/R_2[ln(I_{C1}I_{S2}) - ln(I_{C2}I_{S1})]$

$=V_T/R_2 \ln(I_{C1}I_{S2}/I_{C2}I_{S1})$

Where  $V_T$  is the thermal voltage.

The condition makes the estimate that the currents are both much bigger than the scale currents, IS1 and IS2.

#### 2. Wilson current mirror

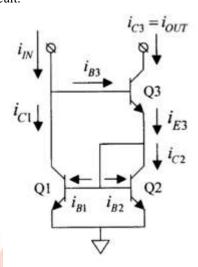

A Wilson current mirror is a three terminal circuit.

Figure-2

In fig.-2 ,transistor Q1 and Q2 are a matched pair sharing the same emitter and base potentials and therefore have  $i_{C1} = i_{C2}$  and  $i_{B1} = i_{B2}$ . This is a basic two transistor current mirror with iE3 as its input and iC1 as its yield. When a current  $i_{in}$  is applied to the input node, the voltage from that node to ground begins to increase. As it surpasses the voltage required to inclination the emitter-base intersection of Q3,Q3 goes about as an emitter supporter or normal gatherer intensifier and the base voltage of Q1 and Q2 starts to rise. As this base voltage increases, current of Q3 precisely adjust iin. Under this condition every one of the three transistors have almost break even with authority streams and therefore approximately equal base currents. Let  $i_B = i_{B1} = i_{B2} = i_{B3}$ . Then the collector current of Q1 is  $i_{in}$  -  $i_B$ . The collector current of Q2 is precisely equivalent to that of Q1 so the emitter current of Q3 is  $i_{E3} = i_{C2} + 2i_B = i_{in} + i_B = i_{in} + i_B$

The collector current of Q3 is its emitter current less the base current so

$i_{out} = i_{in} + i_B - i_B = i_{in}$  .In this approximation static error is zero.

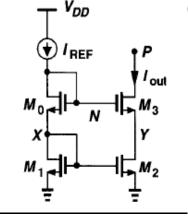

# 3. Cascoded current mirrors

So as to smother the impact of channel-length modulation, cascade current source can be utilized. Legitimate decision of measurements of M0 as for those of M3 yields  $V_{GS0} = V_{GS3}$ . Connecting the node N to the gate of M3 as shown in figure-3.

Figure-3

We have VGS0 + VX = VGS3 + VY. Thus if,

$(W/L)_3 (W/L)_0 = (W/L)_2 (W/L)_1$

There  $V_{GS3} = V_{GS0}$  and

$V_X = V_{Y}$

Note that this outcome regardless of the fact that M0 and M3 experiences body effect. While working as a current source with high yield impedence and exact estimation of topology of figure-3, nonetheless devours significant voltage headroom.

## III. BULK-DRIVEN MOSFET CURRENT MIRROR FOR CMOS TECHNOLOGY

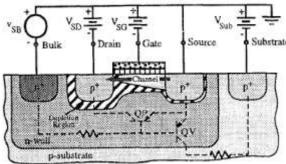

This bulk-driven MOSFET current mirror is capable of operating with threshold voltages in the range of +0.8V and power supplies down to 1V. The requirement that the input voltage of the current mirror equals  $V_{GS} > V_T$  is removed in this bulk-driven MOSFET configuration. In this paper, the operation and first order models for the bulk-driven MOSFET is presented along with the experimental results and the operation of a simple bulk-driven mirror. The bulk-driven technique can only be applied to the MOSFET which can be fabricated in its own separate well. Figure-4 shows the p-type MOSFET's cross-section. In the figure, the parasitic lateral (QP) and vertical (QV) bipolar junction transistors are shown. The operation of bulk-driven MOSFET is almost same like a JFET. By connecting the gate terminal to a fixed voltage of sufficient magnitude, will establish the inversion layer forming the conduction channel beneath to form a channel. The MOSFETs inversion layer beneath the gate structure is the conduction channel of JFET. The bulk potential determines the thickness of the inversion layer, drain and the depletion of the layer beneath the source of the MOSFET. The depletion layer thickness changes by varying the bulk-source voltage, and the inversion layer through which the drain current is flowing is modulated. With a very small dc values of the bulk-source potential, the channel current can be modulated and this results in a device that is extremely useful for low voltage applications.

Figure-4

The current mirrors present days contains the gate-drain or diode connections and for the strong inversion saturation operation, the voltage drop across this connection is greater than  $|V_T|$ . To keep away from the extensive voltage drop penalty, the bulk driven

current mirror is talked about in this paper.

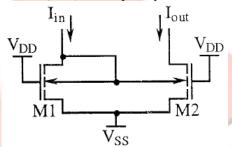

Figure-5

In Figure-5,NMOS bulk-driven current mirror is shown. In this, the gate-drain diode connections in the simple current mirror is not used instead of that the bulk-drain connection is used. Rather than the gates, the bulks of transistors M1 and M2 are tied together. The gates of M1 and M2 is connected to the most positive fixed voltage available, VDD. To form the inversion layer beneath the gate, the voltage potential between each gate and source must be greater than or equal to 1V. These NMOS version current mirrors are suitable for low power supply voltage applications.

#### IV. CONCLUSION

The above paper reviews the current mirror and its various functions. Different types of current mirrors are also shown in this paper with their operations. Bulk Driven MOSFET current mirror for CMOS innovation with low voltage is likewise examined. In the future scope, the bandwidth of this current mirror can be enhanced and the supply voltage can also be decreased so that it can be suitable for low supply voltage applications.

#### V. REFERENCES

- [1] B. Razavi, Design of Analog CMOS Integerated Circuits, McGraw-Hill.

- [2] N. Mahajan, "A Low-Voltage Low-Power Self Biased Bulk-Driven PMOS Cascade Current Mirror", IEEE ICRITO.

- [3] B. Minch, "Low-Voltage Wilson Current Mirrors in CMOS", IEEE ISCAS, New Orleans, LA, USA, 2007, pp. 2220-2223.

- [4] M.K. Priya, V.K. Vanitha Rugmoni, "A Low Voltage Very High Impedance Current Mirror Circuit and Its Applications", IEEE ICCCE, 2013, pp. 511-516.

- [5] E. Raghuvaran, "A Very High Impedance Current Mirror For Biomedical Applications", IEEE Transactions on Analog Circuits, 2011,pp 828-830.

- [6] B. J. Blalock, and P.E. Allen. "Low-Voltage, Bulk-Driven MOSFETCurrent Mirror for CMOS Technology," IEEE ISCAS I995,vol. 3, pp.1972-1975, 1995.

- [7] B. A. Minch, "A Low-Voltage MOS Cascode Bias Circuit for All Current Levels," in Proc. ISCAS'02, vol. 3, Phoenix, AZ, May 2002, pp. 619–622.

- [8] A.P. Chandrakasan, S. Sheng, and R.W. Brodersen, "Low-Power CMOS Digital Design," IEEE JSSC, Vol. 27, No. 4, pp. 473-484, April 1992.