# Optimization Of A Four Bit Digital Multiplier Design Using Mosfet And Finfet Technology

Farhana Hamid Bhat<sup>1</sup>, Er Ari Goel<sup>2</sup> <sup>1</sup>M.tech Scholar, <sup>2</sup>Assistant Professor, ECE Department, SDDIET, Barwala, Haryana, INDIA

Abstract - In this paper, a low power ultra-high speed multiplier is proposed by utilizing voltage scaling system for FinFET dual mode technique. A Multiplier design is implemented in MOSFET 32nm and also in FinFET 32nm, performance is compared on the basis of Average power Consumption and Delay. A variation of Number of fins versus Average power is also calculated. Simulation results are obtained using Synopsys HSPICE software, and they show that dual mode multiplier technique is low power. Delay is also improved when FinFETs are used in the Multiplier.

Keywords - Multiplier, Dual Mode, FinFET, 32nm

#### 1. Introduction

As nanometer process innovations have propelled, chip thickness and working recurrence have expanded, making power utilization in battery-worked versatile gadgets a noteworthy concern. Notwithstanding for non-compact gadgets, control utilization is vital on account of the expanded bundling and cooling costs and also potential unwavering quality issues. [3]Along these lines, the principle outline objective for VLSI (extensive scale) architects is to meet execution necessities inside a power spending plan. In this manner, control effectiveness has expected expanded significance.[1] This undertaking investigates how circuits in view of FinFETs (blade write field-impact transistors), a rising transistor innovation that is probably going to supplement or supplant mass CMOS (corresponding metal-oxide-semiconductor) at 22-nm and past, offer intriguing delay–control tradeoffs. [2]

The desire to improve the plan measurements of execution, control, territory, cost, and time to advertise (opportunity cost) has not changed since the origin of the IC business. Truth be told, Moore's Law is tied in with streamlining those parameters. [6] Be that as it may, as scaling of assembling hubs advanced towards 20-nm, a portion of the gadget parameters couldn't be scaled any further, particularly the power supply voltage, the predominant factor in deciding dynamic power. What's more, enhancing for one factor, for example, execution consequently converted into enormous bargains in different zones, similar to control.[4] Another restriction as procedures moved toward 20-nm was the way that lithography was stuck at ArF brightening source with a wavelength of 193nm while the procedure basic element was pushing sub-20nm. Optical developments, for example, submersion lithography and twofold designing made that conceivable, yet at the cost of expanded inconstancy. There were likewise different advancements en route, for example, high-K metal door that mitigated – to a restricted degree – entryway spillage issues. [5]Be that as it may, the reality remained that the plan window for enhancing among the previously mentioned outline factors was contracting. Outlining in FinFET expands the plan window by and by. Working voltage keeps on downsizing, altogether saving money on unique and static influence. Short channel impacts are lessened fundamentally, diminishing the monitor banding expected to manage inconstancy. Furthermore, execution keeps on enhancing contrasted with planar at an indistinguishable hub. Truth be told, at low power supply voltages, the execution preferred standpoint of the FinFET contrasted with its planar comparable extends because of the unrivaled entryway control of the divert in the FinFET. For memory planners, an additional preferred standpoint of FinFETs is the essentially bring down maintenance voltage prerequisites of FinFET-based Multipliers contrasted with planar FETs. Given the developing metric of execution per unit control (Koomey's Law), one noteworthy outline streamlining advantage of FinFET contrasted with planar is substantially higher execution at a similar power spending plan, or equivalent execution at a much lower control spending plan. This basically enables planners to remove the most astounding execution for the least power, a basic improvement for battery-fueled gadgets.[7][8] One element that makes the progress from outlining with planar FETs to planning with FinFETs somewhat less perplexing is the way that the back-end of the procedure is basically the same, and hence the piece of the outline stream related with the physical execution stays in place. [12]

# 2. FinFET Technology

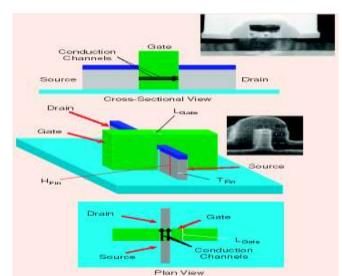

FinFET, otherwise called Fin type Field Effect Transistor, is a kind of non-planar or "3D"transistor utilized as a part of the outline of present day processors. As in prior, planar outlines, it is based on a SOI (silicon on encasing) substrate. In any case, FinFET outlines likewise utilize a directing channel that ascents over the level of the encasing, making a thin silicon structure, molded like a blade, which is known as an entryway terminal.[3] This blade molded cathode enables numerous doors to work on a solitary transistor. Despite the fact that present conduction is in the plane of the wafer, it isn't entirely a planar gadget.[9] Or maybe, it is alluded to as a semi planar gadget, since its geometry in the vertical heading (viz. the balance tallness) likewise influences gadget conduct. Among the DG-FET writes, the FinFET is the least demanding one to manufacture. Its schematic is appeared in Fig.1.[5]

#### **Figure 1 FinFET structure**

As a result of the vertically thin channel structure, it is alluded to as a balance since it takes after a fish's balance; henceforth the name FinFET. A door can likewise be manufactured at the highest point of the balance, in which case it is a triple entryway FET. Or then again alternatively, the oxide over the blade can be made sufficiently thick with the goal that the entryway over the balance is in the same class as not being available. It ought to be noticed that while the door length L of a FinFET is in an indistinguishable sense from that in an ordinary planar FET, the gadget width W is very extraordinary. W is characterized as:

$$W = 2H_{fin} + T_{fin}$$

where Hfin and Tfin are the height and thickness individually (see Fig. 1 above. [8]Some writing alludes to the blade thickness as the balance width). The explanation behind this is very clear when one notification that W as characterized above is in fact the width of the door area that is in contact with (ie. responsible for) the divert in the balance (yet with a dielectric in the middle). This reality can particularly be checked whether one unfurls the door (i.e. unwraps it). [3][4]

# 3. Multiplier

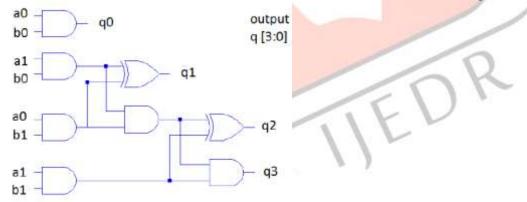

. The subsequent reenactments are ascertained on summation HSPICE by utilizing coding the hubs of the circuit outline, the circuit chart hubs are given extraordinary hub call, for which the FINFET variant from BSIMCMG is covered and simulated. The 4 bit 2 bit op-code selects the result of either logical or arithmetic block to be the output of the Multiplier.

...1

# Figure 2: Four Bit Multiplier Design Block Diagram for Gate Level

#### 4. Simulation Results:

Results are obtained on synopsys HSPICE software and models of FinFET from PTM website, i.e. Predictive Technology Model.

161

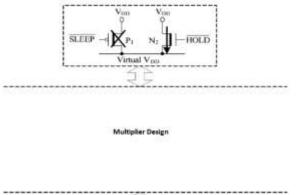

# Figure 3: Dual Mode Multiplier Block Diagram

The Multiplier is implemented on dual mode technique for reduction of power and delay in the circuit. Figure 3 gives block diagram of dual mode technique.

The purpose of adding these additional power gating paths is to provide three modes – active (RUN), intermediate data retention (HOLD) and CUT-OFF.

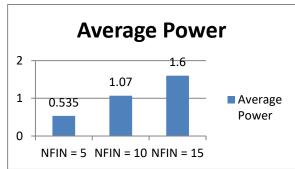

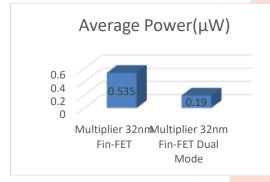

# Figure 4: Multiplier Average Power for MOSFET and FinFET

Figure 4 is representing bar graphical representation of Average power consumption comparison in FinFET device circuit and MosFET device circuit multiplier. The results clearly prove that a lot of power saving and high efficiency can be achieved by the use of FinFET.

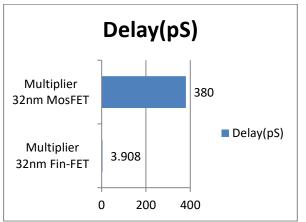

Figure 5: Delay in Multiplier FinFET and Multiplier MosFET

Figure 5 represents delay in Multiplier using FinFET and MOSFET. Table 2 represents results of delay in Multiplier.

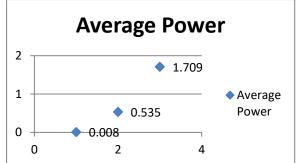

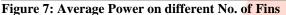

Effect on Average power of change in voltage supply and No. of Fins is shown in Figure 6 and Figure 7.

Figure 6: Average Power on different Vdd

# Figure 8: Improvement in FinFET design using Dual Mode Technique

# **Table 2: Delay Multiplier**

| Metric/Circuit | Multiplier<br>32nm Fin-<br>FET | Multiplier<br>32nm<br>MosFET | 5  | Conclusion |

|----------------|--------------------------------|------------------------------|----|------------|

| Delay(pS)      | 3.908                          | 380                          | 5. | Conclusion |

- Average Power is reduced by in Fin-FET based gates which are used to design MULTIPLIER.

- At 32nm technology, the delay is reduced in FinFET, so device becomes high speed.

- By using Dual Mode technique in Finfet design, average power consumption is reduced.

- Hence, FinFET is a promising substitute for MosFET at lower scaled technology.

# 6. References

[1] Xinfei Guo, Vaibhav Verma" Back to the Future: Digital Circuit Design in the FinFET Era" Journal of Low Power Electronics Vol. 13, 1–18, 2017

[2] Manisha Jayson, Anitha Senthil Kumar, "FinFET technology and its advancements

- -A survey" International Journal of Scientific & Engineering Research Volume 8, Issue 6, June-2017

- [3] Sarada Musala, Student Member, IEEE, "FinFET Based 4-BIT Input XOR/XNOR

Logic Circuit", IEEE, 2016

[4] Zhichao Lu, IEEE, Vol 28, Feb- 2007, "Short Channel Effects in FinFet"

[5] Ajay N. Bhoj and Niraj K. Jha, IEEE, 2013, "Design of Logic Gates and Flip-Flops in High-performance FinFet Technology"

163

[6] R.Rajprabu, IOSR-JVSP, Vol 2, Apr- 2013, "Performance analysis of CMOS and FinFet Logic"

[7] Sherif A.Tawfika, Elsevier, 2011, "FinFET domino logic with independent gate keepers"

[8] N.Prathima "Design of a low power and high performance digital multiplier

using a novel 8T adder" IJERA, Feb 2013

- [9] Mahender Veshala, IJEIT 2013, "Reduction of Short-Channel Effects in FinFET"

- [10] V Narendar, IJCA, 2012, "Design of High-performance Digital Logic Circuits based on FinFET Technology"

- [11] PC Rajashree, ICIET-2014, "Deep Submicron 50nm CMOS Logic Design with FINFET"

- [12] Tushar Surwadkar, IJETT-2014, "Upgrading the performance of VLSI Circuits using FinFETs"